The Florida Institute for Cybersecurity Research

**VOLUME II**

- GAINESVILLE, FL

- **352-294-3945**

- FICS.INSTITUTE.UFL.EDU

## **TABLE OF CONTENTS**

| ABOUT FICS RESEARCH  | 3   |

|----------------------|-----|

| TECHNICAL AREAS      | 4   |

| PROJECT TITLES       | 6   |

| PROJECT DESCRIPTIONS | 12  |

| FACILITIES           | 95  |

| BOOKS                | 102 |

| FACULTY BIOS         | 104 |

| SPANSARS             | 118 |

## **ABOUT FICS RESEARCH**

The Florida Institute for Cybersecurity (FICS) Research was established with the mission to become the nation's premier multidisciplinary research institute, seeking the advancement of cyber security as a basis for long-term partnership and collaboration among industry, academe, and government. FICS Research's objective is to directly support the research needs of industry and government partners in a cost-effective manner with pooled, leveraged resources and maximized synergy, as well as to enhance the educational experience for a diverse set of top-quality graduate and undergraduate students. FICS Research will work towards advancing knowledge and technologies in this emerging field, as well as ensure the commercial relevance of the research, by establishing spin off companies via rapid and effective technology transfer.

FICS Research is unique. It is arguably the only institute in the country that provides exceptional expertise in all aspects of cybersecurity and assurance, including hardware, network, mobile, big data, internet of things (IoT), applied crypto, social sciences, law, and more.

#### **DIRECTOR**

#### **Mark Tehranipoor**

Intel Charles E. Young Preeminence Endowed Chair Professor in Cybersecurity ECE Department University of Florida

#### **ASSOCIATE DIRECTOR**

#### **Kevin Butler**

Arnold and Lisa Goldberg Rising Star Associate Professor in Computer Science Associate Professor CISE Department University of Florida

## **TECHNICAL AREAS**

TA1: IoT Security

TA2: Biometrics

TA3: Hardware Security

TA4: Software Assurance / Security

TA5: Network Security

TA6: Applied Crypto / Theory

TA7: Usable Security

TA8: Privacy and Anonymity

TA9: Machine Learning for Cyber Defense

TA10: System Security

TA10.1: Automotive Security

TA10.2: Financial Security

TA10.3: Cyber Physical Systems Security

TA10.4: Bio-medical Systems Security

### **PROJECT TITLES**

- 01. Building a Private Bitcoin Payment Network using Off-chain Links

- 02. Drone ITS: Drone-aided Platform for Enabling Next Generation Intelligent Transport Systems

- 03. Efficient Public-Key Management for Smart Meter Communications

- 04. Lightweight Symmetric Key Management for Low-bandwidth Legacy Environments in Smart Grid

- 05. Mitigating Attacks towards Networked Cyber-physical Systems

- 06. SDN and NFV-based Moving Target Defense for Distributed Denial of Service Attacks

- 07. Vehicular Forensics Via Permissioned Blockchain

- 08. Automated Reverse Engineering of Integrated Circuits

- 09. Non-destructive Bond Pull and Ball Shear Tests for Electronics Quality Assurance and Counterfeit Detection through 3D X-ray Tomography and Finite Element Modeling

- 10. Trojan Scanner: Detecting Hardware Trojans with Rapid SEM Imaging combined with Image Processing and Machine Learning

- 11. Towards Provably Privacy-Preserving Data Analysis with Privacy Filters

- 12. Understanding Machine Learning Leaks: Causes and Defenses

- 13. Attention Based Secure Smart Image Sensor design for High-speed Real-Time secure vision applications.

- Design of Secured MPSoC

- 15. Security in FPGA Accelerated Cloud and Datacenters

- 16. Towards a Practical and Secure FPGA-Based Digital Wallet

- 17. Intel SGX-aided Solutions: FORTIS

- 18. One-Time Programs

- 19. Privacy-Preserving Multiparty Computation

- 20. Vetting Embedded Firmware

- 21. AMS Circuit Obfuscation

- 22. Automated Security Property Mapping for Legacy Designs

- 23. Development of a Static Security Property Database

- 24. FPGA Bitstream Reverse Engineering-Based Device Upgrade

- 25. FPGA Trojan Detection using Static Design Analysis

- 26. Hardware Obfuscation Using HLS

- 27. Identifying Vulnerabilities Introduced by High-level Synthesis

- 28. Information Flow Tracking Based Software Vulnerabilities Detection

- 29. Metric-driven Security Property Verification

- 30. Security Verification of AI Systems

- 31. Security Verification using Formal Methods

- 32. SeRFI: Secure Remote FPGA Initialization in an Untrusted Environment

- 33. Security-preserving Post-silicon Validation and Debug

- 34. Aging-resistant FPGA RO PUF

- 35. Attacks and Countermeasures for Semiconductor IP Protection

- 36. Automated Counterfeit IC Defect Detection

- 37. Automated Non-Destructive PCB Reverse Engineering from X-Ray Computed Tomography

- 38. BLOcKeR: A Biometric Locking Paradigm for IoT and the Connected Person

- 39. Cardiovascular Biometric Authentication, Key Generation, and Presentation Attacks

- 40. Circuit Edit Enabled Trusted Fabrication for Low Volume Products

- 41. Covert Gates: Protecting Integrated Circuits from Reverse Engineering with Undetectable Camouflaging

- 42. Developing Low Cost Electrical Test Methods for Counterfeit FPGA Detection

- 43. EMFORCED: EM-based Fingerprinting Framework for Counterfeit Detection on Remarked and Cloned ICs

- 44. EMFORCED: EM-based Fingerprinting Framework for Remarked and Cloned Counterfeit IC Detection Using Machine Learning Classification

- 45. FORTIS: Establishing Forward Trust for Protecting IPs and ICs in Today's Complex Supply Chain

- 46. Hierarchical Bloom Filter (HBF) Framework for Security, Space-efficiency, and Rapid Query Handling in Biometric Systems

- 47. Intrinsic Memory-based Solutions Against Counterfeit ICs

- 48. Metrics and Benchmarking for Logic Locking and Hardware Obfuscation

- 49. Nanopyramids Optical Scramblers for Protecting Against Backside Probing Attacks

- 50. Obfuscation-based PCB Anti-Reverse Engineering

- 51. PCB Tamper Detection

- 52. A provable-security Treatment of Counterfeiting Problems in Electronics Supply Chain

- 53. RASC: Enabling Remote Access to Side-Channels for Mission Critical Systems

- 54. Recycled/Remarked Detection of Analog/Mixed-Signal ICs via LDO

- 55. EM Side-Channel Based Hardware Security Analysis

- 56. Formal Security Validation on RTL Designs

- 57. Hardware Supported Virtual Machine Security Analysis in Cloud Environment

- 58. IoT Security Vulnerability Database Development

- 59. Logic Obfuscation for IP Protection

- 60. DeepSecurity

- 61. Beomsoo: High Precision Analog Mixed-Signal Circuitry for Counterfeit Detection and Securing Supply Chain

- 62. Cost-effective, Scalable, Portable All Digital Approach for Protection Against IC Recycling and Mitigation of Aging Effects

- 63. A Fully-Digital, Unclonable Security Protocol for Use in Analog/Mixed-Signal Systems

- 64. High Precision Analog Mixed-Signal Circuitry for Counterfeit Detection and Securing Supply Chain

- 65. PCB Assurance & Sensitivity Analysis

- 66. IC Trojan Insertion and Detection

- 67. Leveraging Passive Components in Silicon to Improve Security Merits

- 68. Intellectual Property (IP) Trust Validation using Formal Methods

- 69. System-on-Chip Security Validation using Side-Channel Analysis

- 70. Secure Network-on-Chip Architecture

- 71. Post-Silicon Validation and Debug

- 72. System-on-Chip Validation and Verification

- 73. Age-Targeted Automated Security Cueing Against Web-Based Social Engineering Attacks

- 74. Blind Spots Building Developer Centric Security through Crowdsourcing

- 75. Collaborative: Developer Crowdsourcing: Capturing, Understanding, and Addressing Securityrelated Blind Spots in APIs

- 76. Fine-grained Analysis on Software Senility Towards System Unpredictabilities Attacks

- 77. FIRMA: Personalized, Cross-layered Continuous Authentication

- 78. Focused Security Behavior Nudging via Subliminal Stimuli

- 79. Machine Learning for Cyber Defense

- 80. RanStop: A Hardware-assisted Runtime Crypto-Ransomware Detection Technique

- 81. Security Estimation

- 82. Censorship Evasion

- 83. Hedged Cryptography: Salvaging Security When Randomness Fails

- 84. Security of Data Structures

- 85. A Physical Design Flow against Front-side Probing Attacks by Internal Shielding

- 86. ACED-IT: Assuring Confidential Electronic Designs against Insider Threats

- 87. EOFM-based Clock Reverse Engineering demonstrated on FPGA

- 88. Firmware Security: Obfuscation and System-level Mutual Authentication

- 89. Artificial Intelligence Security

- 90. Attacks on DNN Hardware

- 91. Automated Assessment of Fault-Injection Attacks at the Pre-silicon: Models, Metrics, and Tools

- 92. Built-In Self-Authentication (BISA) and Obfuscated BISA to Counter Hardware Trojan Insertion by Untrusted Foundries

- 93. CAD based solutions to detect and stop optical probing of integrated circuit

- 94. Design of an on-chip security engine

- 95. Detecting Zero-day attacks in SoC

- 96. Electronic Systems Protection throughout the Lifecycle

- 97. Electronics Supply Chain Integrity Enabled by Blockchain

- 98. EMFORCED: EM-based Fingerprinting Framework for Remarked and Cloned Counterfeit IC Detection Using Machine Learning Classification

- 99. EOFM-based Clock Reverse Engineering demonstrated on FPGA

- 100. Firmware Security: Obfuscation and System-level Mutual Authentication

- 101 FPGA as a Service: Security Challenges and Opportunities

- 102. Framework for Automated and Systematic Security Assessment of Modern SoCs

- 103. HARDEN: Hardware-Assisted ML-based Anomaly Detection for Cyber Defense

- 104. Hardware Trojan Detection Through Information Flow Security Verification

- 105. Hardware Trojans in AMS domain

- 106. IoTIC: An Internet of Things Integrity Checker

- 107. ISIP: A Comprehensive Framework for Information Security for Intellectual Property and System-on-Chip Verification

- 108. Near-Field EM for Foundry of Origin Identification

- 109. PCB Trojan Detection and Prevention

- 110. Protecting Obfuscated Circuits against Attacks that Utilize Test Infrastructure

- 111. Protection Against Optical Probing Attacks

- 112. Reverse Engineering of a Neural Network Chip

- 113. Rowhammer Attack: Desirable or Undesirable

- 114. Automated Power Side-Channel Leakage Assessment at RTL

- 115. CAD Framework for Power Side-channel Vulnerability Assessment at Gate Level

- 116. Secure HDL

- 117. Secure Software Validation Tools

- 118. Secure Remote FPGA Initialization in an Untrusted Environment

- 119. SPARTA: Laser Probing Approach for Trojan Detection

- 120. Test-chip Design for Security Assessment

- 121. Universal Security Theory for Evaluation and Design of Nano-scale Devices and for Development of Innovative Security Primitives

- 123. Authenticated Telephony

- 124. Characterizing and Strengthening the Modern Health Ecosystem

- 125. Enhancing Electronic Payment Security

- 126. Internet of Things Lifecycle

- 127. Protecting Data with Mandatory Retention Requirements

- 128. Securing Emerging Digital Financial Systems

- 129. Securing Machine Learning Systems

- 130. Development of a Blockchain Oriented Security Class

- 131. Development of A Hands-on Security Class for Internet of Things

- 132. Drone-aided Platform for Enabling Next Generation Intelligent Transport Systems

- 133. Electronic Payments are Essential to Our Modern Economy.

- 134. Identifying Counterfeit Smart Grid Devices: A Lightweight System Level Framework

- 135. An IoT Fingerprinting Framework Using Inherent Device Characteristics

- 136. Privacy-aware Wearable-Assisted Continuous Authentication Framework

- 137. Securing Sensory Side-Channels in CPS and IoT Devices and Applications

- 138. A Sustainable IoT Software Development Framework for Science and Engineering

- 139. Automatic Author Attribution Via Stylometry

- 140. A Formal Approach to Deception

- 141. Hardware/Software Co-Verification for Security

## **PROJECT DESCRIPTIONS**

#### **01. BUILDING A PRIVATE BITCOIN PAYMENT NETWORK USING OFF-CHAIN LINKS**

Kemal Akkaya and Selcuk Uluagac

While Bitcoin dominates the market for cryptocurrencies, its use in micropayments is still a challenge due to its long transaction validation times and fees. Recently, the concept of off-chain payments are introduced that led to a payment network called Lightning Network (LN). Off-chain links provide the ability to do transactions without writing to Blockchain. However, design still favors fees and is creating hub nodes that defeats the purpose of Blockchain. In addition, it is still not reliable as not all the transactions are guaranteed to be transmitted to their destinations. If current vendors would like to use it, these problems might hinder its adoption. To address this issue, in this paper we advocate creating a private payment network among a given set of vendors that will serve their business needs, just like the idea of private Blockchains. The goal is to build a pure peer-to-peer topology that will eliminate the need for relays and increase the robustness of payments. Using off-chain links as edges and retailers as nodes, the problem is formulated as a multi-flow commodity problem where transactions represent the commodities from various sources to destinations. As the multi-flow commodity problem is NP-Complete, we not only develop an optimization model but also propose a heuristic approach that utilizes shortest path algorithms in a dynamic way by changing the edge weights as payments are made.

## 02. DRONE ITS: DRONE-AIDED PLATFORM FOR ENABLING NEXT GENERATION INTELLIGENT TRANSPORT SYSTEMS

Kemal Akkaya and Selcuk Uluagac

The goal of this project is to utilize Unmanned Air Vehicles (UAVs) (or Drones) to not only to enforce the traffic rules and support the traffic police on ground, but also provide the road users with efficient information on traffic (aka intelligent traffic management). ITS UAVs will be enabled by a Dedicated Short Range Communication (DSRC) interface, for Vehicle to Vehicle (V2) and Vehicle to Infrastructure (V2X) communications. In this project, we first lay out the architectural foundations for communication requirements of UAVs by comparing the performance of LTE and mesh solutions in terms of delay and packet delivery ratio. We then looked into

connectivity maintenance by introducing a form of minimum connected dominating set (MCDS) problem and how to maintain this MCDS set to keep the network connectivity all the time. Finally, we will also consider security and privacy issues. For security, the main challenge is to enable authentication of the users that will control or communicate with the UAVs. For this, we propose using an existing OAuth 2.0 framework. This will be implemented in the devices. We will then consider privacy of the users when UAVs record video for ITS purposes. To this end, we are considering using FHE for the encryption of video so that it will stay and processed as encrypted in the servers. However, video data is huge and FHE already comes with heavy overhead, so we are exploring to extract background of the videos and only focus on objects in the video to be transmitted.

#### **03. EFFICIENT PUBLIC-KEY MANAGEMENT FOR SMART METER COMMUNICATIONS**

#### Kemal Akkaya

Secure smart meter communications rely on keys for encryption, decryption, authentication, and so on, but management of keys is a challenge. This project addresses public key distribution in smart meter networks, and in particular, how to revoke breached and expired public keys. It aims to develop customized solutions for certificate revocation lists (CRLs) management that will secure the communications in Advanced Metering Infrastructure (AMI) with high efficiency. So far, we investigated Bloom filters, and distributed hash tables to replace the CRL with a more efficient approach. In this project, we propose another novel idea to further reduce the size of CRLs by exploiting Cryptographic Accumulators inspired from Blockchain. The concept provides an efficient mechanism to check whether an element is a member of a specific set. Although cryptographic accumulators provide very efficient membership test (i.e., whitelist), we need a scheme that provides a non-membership test (i.e., blacklist) to allow working with conventional CRLs where a certificate is deemed valid if it is not in the CRL. To enable an accumulator with non-membership proof capability, we construct an accumulator scheme that provides a nonmembership witness for each value not in the list. In a nutshell, we propose condensing the entire CRL into single accumulator value to avoid unmanageable CRL size for the smart meters

# 04. LIGHTWEIGHT SYMMETRIC KEY MANAGEMENT FOR LOW-BANDWIDTH LEGACY ENVIRONMENTS IN SMART GRID

Kemal Akkaya

As the utility companies rightly requests to build the new systems on top of the legacy systems with limited investment, the research community needs to re-think the adaptation of the existing security approaches to such non-traditional legacy environments. This project aims to tackle symmetric key management in a severely constrained communication environment in Smart Grid. Assuming a legacy radio communication infrastructure with bandwidths in the order of kilobits, the objective is not only to reduce the number of messages that need to be exchanged but also minimize the size of the packets that are transmitted. Specifically, we aim to bring Quick UDP Internet Connections (QUIC) protocol of Google in resource-constrained environments by eliminating the need for the PKI. For this purpose, we propose utilizing dynamic key generation techniques that applies cryptographic hash function to a key multiple time so that this can be used for future rekeying without any need for signatures. In this way, we will be able to reduce the number of messages and their sizes significantly. In addition, the scheme lowers communication cost by relieving signature requirement in OUIC. Finally, the scheme also addresses the reliability issues without a need to ACK messages or mechanisms such as the ones used in TCP.

#### **05. MITIGATING ATTACKS TOWARDS NETWORKED CYBER-PHYSICAL SYSTEMS**

Kemal Akkaya

Developing security mechanisms for networked cyber-physical systems (NCPS) significantly differs from traditional networked systems due to interdependence between cyber and physical subsystems (with attacks originating from either subsystem), possible cooperation between attackers or defenders, and the presence of human decision makers in the loop. The main goal of this research is to develop the necessary science and engineering tools for designing NCPS security solutions that are applicable to a broad range of application domains. In particular, we experiment traditional DDoS attacks that would result in delaying and packet losses on a two-party NCPS and analyze the behavior on the stability of the control systems. We offer solutions based on game-theory.

# 06. SDN AND NFV-BASED MOVING TARGET DEFENSE FOR DISTRIBUTED DENIAL OF SERVICE ATTACKS

Kemal Akkaya

One of the recent paradigms to provide security is based on the idea of dynamic networks, which is referred to as moving target defense (MTD). MTD aims to provide agility and/or adaptivity to current networks in order to make it harder for the attackers to launch attacks. Since dynamicity and centralized management is utmost important in applying MTD and forensics, the emerging software defined networking (SDN) and network function virtualization (NFV) can be an excellent technology that can be integrated with MTD and forensics systems for efficient and cost-effective operations. SDN is a key in terms of imposing network-wide policies, upgrades and state changes. This project aims to investigate the potential of SDN and NFV in addressing cybersecurity and resilience for the existing enterprise networks and provide a cost-benefit analysis for all the stakeholders involved in such research and development. In particular, DDoS attacks that aim to congest permanent links are considered. New MTD approaches subordinated with SDN will dynamically change the routes by using the generated fake virtual routes, and direct traffic to internal analyzers. In addition to assessing the overhead of network state changes, we also proposed a signaling game-theoretic model for defender-attacker interaction.

#### 07. VEHICULAR FORENSICS VIA PERMISSIONED BLOCKCHAIN

Kemal Akkaya and Selcuk Uluagac,

Today's vehicles are becoming cyber-physical systems that not only communicate with other vehicles but also gather information from hundreds of sensors within them. These developments help create smart and connected (e.g., self-driving) vehicles that will introduce significant information to drivers, manufacturers, insurance companies, and maintenance service providers for various applications. One such application that is becoming crucial with the introduction of self-driving cars is forensic analysis of traffic accidents. The utilization of vehicle-related data can be instrumental in post-accident scenarios to discover the faulty party, particularly for self-driving vehicles. With the opportunity of being able to access various information in cars, in this project we propose a permissioned blockchain framework among the various elements involved to manage the collected vehicle-related data. Specifically, we will first integrate vehicular public key infrastructure (VPKI) to the proposed blockchain to

provide membership establishment and privacy. Next, we will design a fragmented ledger that will store detailed data related to vehicles such as maintenance information/ history, car diagnosis reports, and so on. The proposed forensic framework enables trustless, traceable, and privacy-aware post-accident analysis with minimal storage and processing overhead

#### **08. AUTOMATED REVERSE ENGINEERING OF INTEGRATED CIRCUITS**

Navid Asadi, Domenic Forte and Mark Tehranipoor

Deprocessing of ICs historically employs a variety of mechanical and chemical process tools in combination with one or more imaging modalities to reconstruct the IC architecture. In this project, we explore the development of an extensible programmatic workflow which can take advantage of evolving technologies in 2D/3D imaging, distributed instrument control, image processing, as well as automated mechanical/chemical deprocessing technology. Areas as large as 800umX800um were deprocessed on a 65nm node 3.0 cm2 Opteron IC processor chip using gasassisted plasma FIB delayering. Ultrathinning the silicon substrate in the packaged device within 1-2um of the IC device significantly reduces the amount of time required for deprocessing. The computer aided backside ultra-thinning approach not only improves the success rate, as compared to manual techniques, it also allows the dense lower layers with smallest feature size to be imaged via high resolution SEM first, while the sample layers are the most uniform. Backside deprocessing has the additional advantage that it can be possible to access the device while keeping it "alive" for in-situ electrical testing. Ongoing work involves enhancing the deprocessing workflow with "intelligent automation" by bridging FIB-SEM instrument control and near real-time data analysis to establish a computationally guided microscopy suite. A common python scripting API architecture between the FIB-SEM platform and the image processing and microanalysis platforms permit rapid development of customized programmatic instrument control with data process integration and feedback. We are able to demonstrate, for the first time, tomographic reconstruction based upon automated backside ultra-thinning coupled to automated gas-assisted plasma FIB delayering.

# 09. NON-DESTRUCTIVE BOND PULL AND BALL SHEAR TESTS FOR ELECTRONICS QUALITY ASSURANCE AND COUNTERFEIT DETECTION THROUGH 3D X-RAY TOMOGRAPHY AND FINITE ELEMENT MODELING

Navid Asadi and Mark Tehranipoor

The lack of trust in foreign and third party entities combined with the prevalence of counterfeit electronics in today's supply chain have increased the need for acceptance tests by the original equipment manufacturers (OEMs) who are responsible for supplying electronic systems in critical applications. Among the many tests, inspection of wire bonds and ball grids are two of the most important. Wire bond related failures contribute to more than 25% of total reliability problems of electronics packages from manufacturing and testing. To perform conventional bond pull and bond ball shear tests, a chip has to be decapsulated either locally or entirely in order to get access to the bond wires. However, this process is destructive and slow. X-ray tomography and Finite element modelling (FEM) can help us speed up the above testing procedure and make it non-destructive. For the first time, we have introduced a new approach based on 3D X-ray tomography and FEM to simulate and analyze the integrity of a real bond-wire without the need to physically decapsulate the chip. This approach enables us to perform a variety of "virtual" tests on the same piece nondestructively.

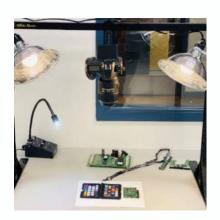

# 10. TROJAN SCANNER: DETECTING HARDWARE TROJANS WITH RAPID SEM IMAGING COMBINED WITH IMAGE PROCESSING AND MACHINE LEARNING

Navid Asadi and Mark Tehranipoor

Trojans are malicious changes to the design of integrated circuits (ICs) at different stages of the design and fabrication processes. Different approaches have been developed to detect Trojans namely non-destructive (electrical tests like run-time monitoring, functional and structural tests) and destructive (full chip reverse engineering). However, these methods cannot detect all types of Trojans and they suffer from a number of disadvantages such as slow speed of detection and lack of confidence in detecting all types of Trojans. Majority of hardware Trojans implemented in an IC will leave a footprint at the doping (active) layer. In this paper, we introduce a new version of our previously developed "Trojan Scanner" framework for the untrusted foundry threat model, where a trusted GDSII layout (golden layout)

is available. Advanced computer vision algorithms in combination with the supervised machine-learning model are used to classify different features of the golden layout and SEM images from an IC under authentication, as a unique descriptor for each type of gates. These descriptors are compared with each other to detect any subtle changes on the active region, which can raise the flag for the existence of a potential hardware Trojan. The descriptors can differentiate variation due to fabrication process, defects, and common SEM image distortions to rule out the possibility of false detection. Our results demonstrate that Trojan Scanner is more reliable than electrical testing and faster than full chip reverse engineering. Trojan Scanner does not rely on the functionality of the circuit rather focuses on the real physical structure to detect malicious changes inserted by the untrusted foundry.

#### 11. TOWARDS PROVABLY PRIVACY-PRESERVING DATA ANALYSIS WITH PRIVACY FILTERS

#### Vincent Bindschaedler

Companies routinely want to share sensitive data or data analysis results with the public and other organizations. But due to privacy concerns and legal considerations, such sharing is often limited or prohibited. As a result, there is tremendous desire to find technical solutions, particularly ones that provide formal privacy guarantees such as differential privacy. Existing techniques mostly consist of adding noise to the data (before or after analysis) but this often leads to unacceptable quality loss. This project proposes and explores a novel way to design privacy-preserving algorithms for data sharing and data processing tasks with privacy filters. A privacy filter is a rejection-sampling based technique that systematically identifies and discards outputs or results that leak sensitive information and lead to privacy violations. Our initial work demonstrates the use of privacy filters for sharing sensitive data through data synthesis with arbitrary generative models. Continuing work will explore the use of privacy filters as a general design pattern for privacy-preserving data processing algorithms in various contexts.

#### 12. UNDERSTANDING MACHINE LEARNING LEAKS: CAUSES AND DEFENSES

Vincent Bindschaedler

The increasing popularity of machine learning and AI has unearthed new security and privacy threats. These threats are often due to strange and unexpected behaviors of popular machine learning techniques. For example, deep neural networks often unintentionally memorize (part of) their inputs which allows attackers to maliciously probe these models and extract information about their sensitive training data. This is of particular concern given that companies and organizations increasingly want to share or publish models instead of raw data. Existing solutions such as differential privacy model training do not always scale to complex models without incurring a prohibitive decrease in model performance. Moreover, the extent of the leakage and its root causes remain poorly understood. In particular, preliminary results reveal that overfitting is a sufficient but not a necessary condition for such memorization. The goal of this ongoing project is to understand the fundamental causes of this unintended memorization behavior and eventually to design effective mitigation strategies.

#### 13. ATTENTION BASED SECURE SMART IMAGE SENSOR DESIGN FOR HIGH-SPEED REAL-TIME SECURE VISION APPLICATIONS.

Christophe Bobda

With the increase in image size, sequential image processing on an external processor, and the data transfer time from the sensor to a processor are increasing. Besides, when the sensor sends data, the data confidentiality becomes questionable. Hence traditional commercial CMOS image sensor does not suffice for edge computing where higher resolution and high-speed, secure video processing is inevitable. The goal of this research is to present a secure in-sensor architecture to extract local features in parallel and establish secure communication with an external processor to achieve high acceleration for vision applications. To achieve this milestone, we propose a computational layer in parallel with the image sensor (recently developed by sony). This layer divides the image into several logical regions and has a region processing unit (RPU) for each region. The RPU is a coarse-grain reconfigurable processor and stands to extract local features in parallel. An attention module and a crypto core reside in each RPU. In the attention module, we implement predictive coding, which is observed in our visual systems. It calculates the visual

saliency and stands to activate the RPU processing and the crypto core. If the corresponding region has salient information, then the RPU extracts local features, and the crypto core encrypts the data and sends the ciphertext to the external processor. Notably, all crypto cores in the design have different encryption keys to enhance security. Alternately, if a region does not have enough visual information, our architecture skips the data transfer from that region and helps to reduce data volume. The feature data that is transferred is not continuous but discrete. Hence, the design becomes highly secure because of the attention bases system encrypts discrete data with different encryption keys. The external processor then receives the encrypted features and executes the remainder operation in vision applications. Since the processor receives only feature data in a reduced form, the remainder operation can be completed fast on a sequential processor to ensure high-speed processing of a machine vision application. We are currently prototyping the design in FPGA and ASIC platforms. Our future target is to investigate the machine learning algorithms for near sensor processing and develop an architecture to make the sensor more secure.

#### 14. DESIGN OF SECURED MPSOC

#### Christophe Bobda

Security has become one of the most crucial parts of Multi-processor System-onchip (MPSoC) design because of its usage in the internet of things (IoT) devices, cyberphysical systems, and embedded computing systems. The ever-increasing complexity of on-chip components and long supply chain make SoCs vulnerable to hardware and software attacks. These attacks can be originated either from inside the chip or from malicious software components. To mitigate hardware originated attacks, we propose Hardware Sandbox concept which can be used for secure operation of non-trusted IPs in SoC. Besides, accessing custom hardware IPs in FPGA accelerated SoCs are not controlled by the Operating system. Hence, software originated attacks such as confidential information leakage and denial of service attacks can be launched on those IPs. We propose a hardware isolation approach to ensure controlled access to hardware IPs in the FPGA part of an SoC. The access to an IP is enforced through the Hardware Management Module (HMM) which is a hardware-software co-design and works with the Flask security architecture integrated into the operating system. The benefit of using this security framework is less area overhead and can be easily integrated into the system. We implemented a prototype of our security framework on Zybo Z7-10 with an onboard Zyng SoC with its corresponding petalinux OS image. Currently, we are working on developing the

MeXT-SE tool that can generate platform-independent and secured multi-processor systems from a high-level abstraction. The aim of this work is to ease the implementation of an adaptive multiprocessor system while ensuring security. The proposed design flow starts with a set of abstract and concrete specifications of a system, provided by the user, and ends up generating a generic description of the appropriate hardware design by setting up the communication structure of different components. The resulting abstract architecture is further processed using the vendor tool-chain to generate the target platform's configuration. The generated MPSoC design enforces security by implementing the above mentioned distributed isolation framework to control access of FPGA accelerators in heterogeneous System-on-Chips and is being enforced transparently by the MeXT-SE tool. Our future work focuses on optimizing the MPSoC design considering security in mind.

#### 15. SECURITY IN FPGA ACCELERATED CLOUD AND DATACENTERS

#### Christophe Bobda

Virtualizing resources within cloud infrastructure offers the opportunity to share physical resources between multiple tenants. As such, the overall performance of cloud services is improved since application codes and data can be co-hosted on single hardware. While computing, network, and storage components such as CPUs, GPUs, memories, and routers have well been exploited in the cloud, FPGA virtualization still needs to be assessed. As a matter of fact, though FPGAs can outperform CPUs and GPUs in several applications, they might also lead to security challenges that can potentially put cloud infrastructures and user applications at risk. Indeed, allowing tenants to share and reconfigure FPGA regions at runtime could result in information leakage, side-channel attacks, denial-of-service, or functional alteration of designs co-deployed on a chip. Therefore, we elaborate an FPGA virtualization approach that emphasizes domain isolation between tasks running in a cloud infrastructure from the software down to hardware threads, preventing applications to access or tamper with the execution of tasks in another's domain.

#### 16. TOWARDS A PRACTICAL AND SECURE FPGA-BASED DIGITAL WALLET

#### Christophe Bobda

In today's world where a large portion of our assets are in digital form, special precautions must be taken to ensure sensitive materials are safeguarded with protection. Blockchain technology has driven a new trends with cryptocurrency and enables for users a decentralized way to securely manage digital assets and perform transactions between one another. However, the core of security with most digital assets is the protection of one's keys that limit access to assets to only individuals that hold the cryptographic keys. We set our focus on the development of a more secure and practical hardware wallet for general blockchain assets, with initial attention targeting the Bitcoin cryptocurrency. We propose a hardware wallet based on FPGA that inherits the benefits of hardware implementations while realizing additional FPGA-inherent security measures. We intend to provide the core functionality expected with a wallet in a system-on-chip implementation within reconfigurable fabric, while adding practical features such as wireless BLE communication with a companion application that interfaces with the asset P2P network. Our work has produced an initial prototype hardware wallet on a Zybo Z7-10 with an onboard Zyng SoC and companion mobile application that allows secure Bitcoin transaction signing. We are currently investigating methods for accelerating cryptographic functions with dedicated IP and improving security measures with an SoC implementation that resides solely in programmable logic. Future work aims to expand the scope of targeted digital assets beyond cryptocurrency.

#### 17. INTEL SGX-AIDED SOLUTIONS: FORTIS

#### Kevin Butler

Intel's Software Guard Extensions (SGX) extend the x86 Instruction Set Architecture with new processor instructions and hardware. SGX provides processor-enforced protected regions of memory, or enclaves, to contain sensitive program code and data. Although enclaves run as user mode (ring-3) applications, other applications and privileged code are prevented from accessing enclave memory. We examine black-box modeling of the enclave, viewing it as a trusted computation oracle. Compared to traditional techniques for secure computation which rely on expensive cryptography, such as garbled circuits and homomorphic encryption, unencrypted computation within an enclave is highly efficient by orders of magnitude. A hybrid

scheme combining garbled circuits and SGX is of particular interest, since strong cryptographic guarantees may be needed for the most sensitive portions of programs. We also look at enabling SGX in a practical cloud environment. Containers are lightweight virtualization environments which offer strong security guarantees for the host machine, and they are widely deployed on cloud servers. However, they offer few protections to users. By incorporating SGX, we provide hardware-supported isolation and run-time integrity for user applications running inside containers. Future work will consider other applications of SGX and use of SGX in resource-constrained environments, while revisiting program partitioning and side-channels.

#### 18. ONE-TIME PROGRAMS

#### Kevin Butler

One-time programs were first proposed by Goldwasser et al. in 2008 as programs that should run exclusively on a single input. Besides the resulting output, nothing else about the program is leaked. Such programs have a variety of applications, ranging from transfer of cryptographic ability to electronic cash and even one-time proofs. A key building block of one-time programs are one-time memories, which (similarly to oblivious transfer) release one of two possible values per bit of input, after which the unchosen value is deleted. We propose using Intel Trusted Execution Technology (TXT) to realize the notion of a one-time memory. TXT provides an integrity-protected environment which is inaccessible from the outside. The core of our program is implemented in garbled circuits (necessary to protect the generator's inputs), but the selection of keys by the evaluator is moved into TXT. Together with the Trusted Platform Module (TPM), TXT supports measured launch for integrity checking, and a sealed flag can be used to satisfy onetimeness. Compared to previous implementations, which relied on highly customized hardware, we aim to make onetime programs practical by using readily available technologies. Continuing work will look at additional applications of and threat models associated with one-time programs.

#### 19. PRIVACY-PRESERVING MULTIPARTY COMPUTATION

Kevin Butler

Secure multiparty computation, also referred to as secure function evaluation, aims to allow multiple parties to learn the output of a function which takes in their private inputs. Nothing more should be leaked besides the final output and what can be inferred from the output. This has typically been achieved with the use of slow and expensive cryptography in the form of garbled circuits or homomorphic encryption. Although these methods have become more efficient over time, they still remain impractical for most real-time, online computations, particularly on modestlyprovisioned devices. Additionally, we found flaws in stability and output correctness among the many compilers built for secure computation. Based on these findings, we built Frigate, a garbled circuit compiler that is fully validated using extensive testing and which also greatly outperforms previous circuit compilers. In other work, we tackled the outsourcing of secure computation and efficient representation of circuits. Future work will look at further extension of Frigate. We are also investigating privacy preservation in the dynamic spectrum sensing space. Multiple sensor radios collaborate to localize a transmitting node, but individual sensors should not be linkable back to their measurements. Future work will involve formalizing the security goals and testing alternative protocols.

#### 20. VETTING EMBEDDED FIRMWARE

Kevin Butler

For every visible computer terminal, there are many smaller embedded devices driving everything from user peripherals such as flash drives, mice, and keyboards to internet connected products such as security cameras, thermostats, and home networking equipment. Each separate system runs unique and specialized firmware in order to drive hardware resources, possibly in real-time. Many critical tasks are left to embedded devices, yet many run closed-source software running on top of proprietary or trade-secret hardware. These black-box devices lead to uncertainty and force users to trust the manufacturers and implementers. To regain visibility into normally closed devices, we propose a framework that analyses binary firmware in order to vet it against a set of known security properties. For our first application, we developed FirmUSB to analyze USB device firmware for inconsistencies that could indicate a "BadUSB" attack, which could compromise trusted computer systems at

corporations or government offices. To instrument and understand the firmware semantically, we created a binary to Intermediate Representation (IR) lifter, which allows us to understand the compiled code at a higher level of abstraction.

Our future research includes:

- · Vetting a diverse range of embedded device firmware

- · Supporting additional CPU architectures

- · Improving framework performance and robustness

#### 21. AMS CIRCUIT OBFUSCATION

Farimah Farahmandi and Mark Tehranipoor

As the digital circuits, analog and mixed-signal circuits are also susceptible to various attacks such as counterfeit, overproduction, and Trojan insertion. However, unlike digital circuits, the supply-chain security of AMS circuits has not been fully studied. While different logic locking techniques exist for digital circuits, this is not the case for AMS IPs. In fact, analog IPs are the most counterfeited semiconductor product. Therefore, they are the most vulnerable components in a complex system. Due to the low transistor count of analog ICs, that are vulnerable to IP piracy and reverse engineering of their layouts by malicious foundaries. In this project, we will develop a methodology, metrics, and automated tools for obfuscation of AMS IPs to simultaneously meet the security and performance constraints. We will cover two classes of obfuscation solutions, i.e., (1) pure analog blocks (e.g., amplifiers, voltage regulators, current integrators, etc.) and (2) mixed-signal blocks. We will develop an obfuscation process that relies on locking and modification of the digital part for both above mentioned analog IPs. In this project, we will develop analog obfuscation methods and assessment metrics using programmable passives-based methods as well as digital and mux-based locking techniques. We will also establish metrics and a CAD framework for automatic obfuscation and perform a comprehensive security assessment, using both simulation and test chip fabrication.

#### 22. AUTOMATED SECURITY PROPERTY MAPPING FOR LEGACY DESIGNS

Farimah Farahmandi and Mark Tehranipoor

The usage of system-on-chip has been getting a lot of attraction in safety- and mission-critical system. This system requires a strict security requirement due to the fact that the failure of this kind of system causes severe consequences. It has also been shown that security vulnerabilities can be introduced in different stages of hardware design. This leads to the necessity of developing a technique that can ensure security in every abstraction level of the design. Towards this goal, we aim to verify the design against rigorous security properties at every abstraction level of the design. However, one bottleneck is generating security properties for each abstraction level. To mitigate this issue, we will develop an automatic security property mapping framework that translates the security property from one abstraction level to another. The framework helps to reuse the developed security property in one abstraction level to another and greatly reduce the time to regenerate properties for every abstraction level.

#### 23. DEVELOPMENT OF A STATIC SECURITY PROPERTY DATABASE

Farimah Farahmandi and Mark Tehranipoor

With the increasing design complexity of SoCs, it has become very difficult for the design engineers to manually analyze design implementation weaknesses in order to detect vulnerabilities at a lower level of abstractions. Therefore, design houses which are concerned about security, need to maintain a large group of experts to analyze potential security issues. Such a manual approach is both time-consuming and expensive. All these issues highlight the necessity for generating a comprehensive set of security properties that a design must hold to pass security assessment. In this project, our goal is to develop an architecture agnostic static security property database, based on different security assets in various design abstractions and probable vulnerabilities which the assets can encounter during design and deployment stages. Verification engineers can map the security properties from the database into assertions and feed the assertions to different formal (e.g., equivalence checker, theorem prover, model checker) and simulation-based approaches to perform security verification and validation. Moreover, design engineers can use the database as a guideline to ensure security in the design stage. The security property database will be utilized to develop security metrics for security evaluation of design,

both quantitatively and qualitatively. The coverage and severity of the identified security properties can be used as metrics for security verification closure. For a design with weak security, a designer can go back and modify the design to address the detected security vulnerabilities.

#### 24. FPGA BITSTREAM REVERSE ENGINEERING-BASED DEVICE UPGRADE

Farimah Farahmandi, Fahim Rahman and Mark Tehranipoor

Field Programmable Gate Arrays (FPGAs) are widely deployed in numerous mission-critical systems, such as cloud infrastructures, aerospace, and military applications, due to their reconfigurability and short time-to-market. For higher security and performance, there are practical requirements for upgrading the FPGA devices that remain in the field for many years to more advanced ones. However, the source code of the old FPGAs may not be available today because of the poor management, which hinders the upgrade of the devices. Therefore, it is crucial to find a way to recover the functionally equivalent synthesizable RTL (register-transfer-level) code from the bitstreams of the obsolete FPGAs. In this project, we will study the FPGA architecture of various Xilinx FPGA families and the compositions of corresponding bitstreams (note that the bitstream format is proprietary and undocumented). Next, we will propose schemes on how to reverse engineer bitstreams to their functionally equivalent RTL code and then resynthesize the code to migrate the same design to the new devices. Finally, we will develop a tool to upgrade the devices automatically.

#### 25. FPGA TROJAN DETECTION USING STATIC DESIGN ANALYSIS

Farimah Farahmandi and Mark Tehranipoor

Nowadays, Field Programmable Gate Arrays (FPGAs) have already served as the reconfigurable hardware platforms for various applications, ranging from low-cost consumer electronics to high-end military systems. However, the security concerns regarding FPGA devices are increasing because hardware Trojans can be inserted into them, not only at the design/fabrication phases but also at deployment stages by tampering configuration bitstreams. Dynamic detection methods like side-channel analysis always call for golden models, and they may not be effective if the Trojan is very tiny. On the other hand, code/netlist-based static detection methods show a promising direction to address FPGA Trojan threats since they can analyze the features of the whole design directly. Nevertheless, in most cases, only the low-level

binary FPGA bitstream files rather than high-level code/netlist are available. Therefore, in this project, we will recover the high-level design information (code/netlist) from FPGA bitstream. Also, we will develop efficient FPGA Trojan detection schemes to identify the malicious logics hidden in the recovered design.

#### **26. HARDWARE OBFUSCATION USING HLS**

Farimah Farahmandi and Mark Tehranipoor

High-level synthesis (HLS) has been proven to be an effective solution to address the ever-growing demand for increasing design and verification productivity of the semiconductor design flow. Being extensively matured since its introduction, HLS provides a superior capability to raise design abstraction and produce hardwareindependent design specifications with less complexity for ASIC and FPGA implementations. There are fundamental differences in code execution, management of variables, and control flow between high-level languages and translation tools. These differences facilitate a huge scope to obfuscate designs to make it more robust against conventional attacks. A higher abstraction model can be beneficial in blending the key in the control flow better, and the number of optimization levels will increase, which can mask the sensitive details of the design better. Also, data flow can be made implicit if necessary, using combined techniques in the higher abstraction, which was not possible at the gate level. In this project, we are working on testing cases of different techniques for inserting keys into different entry points of C/C++ codes and evaluating the performance in terms of overhead (area, power) and attack resiliency. The final goal is to identify the best way to obfuscate the higher-level abstraction and create specific rules that need to be followed for it.

#### 27. IDENTIFYING VULNERABILITIES INTRODUCED BY HIGH-LEVEL SYNTHESIS

Farimah Farahmandi and Mark Tehranipoor

High-level synthesis (HLS) has gained much popularities in recent years as it significantly reduces time-to-market by directly translating codes developed in high-level software language, e.g., C to synthesizable hardware designs. Although there have been many works on improving the high-level synthesis process (in terms of performance, area, and power), none have investigated potential security vulnerabilities introduced by HLS. In this project, we are investigating vulnerabilities introduced by the HLS, which could be exploited by attackers to gain access to the

assets in hardware design. Our objective is to identify the coding practices and HLS settings, which leads to security vulnerabilities and then develop a guideline to guide design engineers what to do (Do-s) and not to do (Don'ts) during high-level design implementation and HLS.

#### 28. INFORMATION FLOW TRACKING BASED SOFTWARE VULNERABILITIES DETECTION

Farimah Farahmandi, Fahim Rahman and Mark Tehranipoor

Buffer and integer overflow vulnerabilities and exploitations pose major security threats in the modern computing era. For example, buffer overflow alone accounts for approximately half of prevailing security vulnerabilities. Such vulnerabilities cause arbitrary code executions, denial of service attack (DoS), unauthorized accesses, and the leakage of secret information to unauthorized parties. However, there is a scarcity of efficient and static formal analyzers for software vulnerabilities detection; instead of some run-time solutions are available. The existing run-time solutions overlook most of the practical scenarios of buffer and integer overflow cases. At the same time, they also create large memory overhead with reduced performance and verify only a few execution paths. As a result, the existing solutions are not suitable, especially for low-end embedded systems. In this project, we develop an efficient solution to detect the critical buffer and integer overflows. We integrate the dynamic information flow tracking along with the formal verification (model checking) approach. In the scheme, while the information flow tracking technique tracks untrusted data that are used in array index/loop bound (which may cause Buffer Overflow or Integer Overflow), the model checker traverses all possible paths to find out all critical vulnerabilities and provides formal proof of vulnerabilities in static time.

#### 29. METRIC-DRIVEN SECURITY PROPERTY VERIFICATION

Farimah Farahmandi and Mark Tehranipoor

Security of a system on chip (SoC) can be weakened by exploiting information leakage, timing and power side-channel attacks, design-for-test (DFT) structures, faultinjection attacks, malicious modification during design and manufacturing process, etc. Apart from the vulnerabilities exposed by these attacks, many security vulnerabilities in SoCs can be unintentionally created by designers' mistakes and the designers' lack of understanding of security issues and unsafe design practices. Moreover, computer-aided design (CAD) tools can introduce additional vulnerabilities

in the SoCs while performing power and performance optimizations. These vulnerabilities creates an increased need for a comprehensive security verification and validation efforts. In this project, we develop metrics for quantitative security assessment in the pre-silicon design stage. Depending on security assets, design attributes, associated vulnerabilities, and potential threats, as well as abstraction levels (e.g., RTL, Gate level, Layout), that can be used for security verification and validation.

#### **30. SECURITY VERIFICATION OF AI SYSTEMS**

#### Farimah Farahmandi

With the prevalence of machine learning algorithms, there will be more and more SoCs that contain a dedicated AI accelerator. Compared to traditional SoCs, neural engines improve the intelligence of SoCs and open more backdoors for security issues as well. There may be a limited control on what AI systems learn and policies they internalize in their learning process. AI learns a task through objective functions. Defining objective functions to reflect security concerns and verification is of high importance. If the objective function does not cover all aspects of security requirements and the correct functionality, there is a chance that AI learns vastly different concepts and ends up in unwanted situations. Further, AI may internalize some sensitive information which is decodable by reverse engineering. In this project, we propose designing new policies and quantitative methods to measure the level of trust of the design. We also propose new validation solutions using combining formal methods and test generation techniques to verify security properties of the design.

#### 31. SECURITY VERIFICATION USING FORMAL METHODS

#### Farimah Farahmandi

With the globalization of the IC industry, the outsourcing and integration of third-party hardware Intellectual Property (IP) blocks have become a common practice for System-onChip (SoC) design. However, it raises significant security concerns as an attacker can insert malicious components in third-party IPs and tamper the system. Therefore, using the conventional validation method is not effective in detecting malicious functionality. From the security point of view, it is important to prove that the design implementation is equivalent to its specification, nothing more, nothing less. However, existing formal methods can lead to a state-space explosion when

complex and large IPs are involved. In this project, we develop efficient, formal techniques to identify various potential threats in third-party IPs, analyze their vulnerabilities using theoretically defined metrics, and formally detect them. In this research, we effectively utilize three widely used formal methods (equivalence checking, model checking, and theorem proving) for scalable security validation.

#### 32. SERFI: SECURE REMOTE FPGA INITIALIZATION IN AN UNTRUSTED ENVIRONMENT

Farimah Farahmandi and Mark Tehranipoor

The functionality of an FPGA is completely defined in its binary configuration bitstream. The bitstream is often protected by encryption. The encryption key, as a root of trust, is stored in the non-volatile memory inside the FPGA to defend against various attacks like bitstream reverse engineering, tampering, and cloning. For low cost and short time-to-market, trusted system designers often rely on a potentially untrusted system assembler to buy components, assemble the system and share the encryption key to load the bitstream into the FPGA. However, since the assembler is untrusted, the key sharing process may result in secret leakage and thus the security of the entire bitstream is threatened by enabling attacks such as hardware Trojan insertion and bitstream tampering. Therefore, it is important to guarantee the security of sharing the encryption key between the trusted designers and the FPGAs through untrusted assemblers. In this project, we will propose the communication protocol which can transmit the encryption key securely from a trusted system designer into an FPGA in physical possession of an untrusted system assembler.

#### 33. SECURITY-PRESERVING POST-SILICON VALIDATION AND DEBUG

Farimah Farahmandi and Mark Tehranipoor

Due to the stealthy nature and practically infinite space of malicious functionality as well as design complexity and shrinking time-to-market, a cleverly inserted malicious functionality in a large SoC is highly likely to evade conventional post-silicon validation approaches. In this project, we propose novel post-silicon security validation techniques to ensure the security and trust of silicon designs based on coverage analysis, penetration tests, and data analysis. Currently, there is no effective way to collect coverage of security properties and requirements directly and independently on silicon. We explore how to utilize on-chip design-for-debug infrastructure effectively (e.g., trace buffer and scan chain) to improve the observability of security

properties while preserving the confidentiality requirements of the design. There is an inherent conflict between increasing observability and security. We also propose secure architectures for design-for-debug that do not violate any security constraints by effectively utilizing information flow tracking as well as sidechannel analysis. Moreover, this project aims to explore scrambling and encryption methods to protect the data stored in the trace buffers to prevent information leakage.

#### **34. AGING-RESISTANT FPGA RO PUF**

#### Domenic Forte

Temporal variations like temperature, supply voltage and environmental noise, and silicon aging make it challenging for physical unclonable functions (PUFs) to produce reliable signatures. In the case of FPGA, the problem is even worse since the internal architecture of FPGA is a black box where layout/gate level design alterations are out of the user's hands. Though aging resistant ring oscillator (RO) PUFs have been proposed previously for ASIC design, implementing the same techniques in FPGA is impossible as it involves redesigning the circuit at transistor level. In this project, we are developing the first aging resistant RO PUF design on FPGA. Our approach exploits unused resources in FPGA look up tables (LUTs) to (i) reduce aging degradation and (ii) increase the homogeneity in RO aging. By improving PUF reliability, we can also signature leakage resulting from reduce the hardware overheads and implementations of error correcting codes (ECC). Initial experiments from Spartan 3A FPGA boards demonstrate that our proposed RO PUF is less affected by aging, with the reliability increasing by 37.4% on average. Moreover, by comparing our design with conventional RO PUF in FPGA, the aging degradation decreases by 37% as well.

#### 35. ATTACKS AND COUNTERMEASURES FOR SEMICONDUCTOR IP PROTECTION

Domenic Forte and Mark Tehranipoor

Semiconductor intellectual property is undoubtedly one of the most valuable assets for any electronic design company, requiring enormous amounts of time, monetary investment, research, and development. However, such IPs can be compromised at various steps in the design process, most notably during fabrication at an untrusted foundry, and in the supply chain by reverse engineering attacks. Logic encryption has emerged as a promising solution that enables an IP owner to 'lock' their IP so that unauthorized parties are unable to engage in piracy or theft. However, such

techniques are vulnerable to a wide array of attacks that either circumvent the locking mechanism or compromise the key required to unlock the IP or IC. In CHES '17, we showed that such locking techniques, in spite of being secured by key protection techniques, are vulnerable to functional circumvention or bypass attacks. In light of this and numerous concurrently proposed attacks, we have identified binary decision diagrams (BDDs) as an appropriate framework for evaluating logic locking against different attacks. Our current work in this domain revolves around (i) functional locking techniques with BDD at RTL and netlist levels; (ii) evaluating trade-offs in overhead vs. security, (iii) extending combinational locking techniques to sequential circuits, and vice versa.

#### **36. AUTOMATED COUNTERFEIT IC DEFECT DETECTION**

Domenic Forte, Mark Tehranipoor, Navid Asadi and Damon Woodard

In the past decade, electronics counterfeiting has reached a new level of sophistication. With improved replication techniques and the growing reliance on electronic systems worldwide, the possibility of important systems becoming compromised increases every day. In 2011, it was revealed that the Navy's submarine hunter aircraft had compromised ice detection systems. Additionally, in 2014, the Navy's nuclear submarines were discovered to use counterfeit electronic parts. Because these parts can allow backdoor access, it becomes prudent to vet the parts being used in important systems. Standard procedures involve manual examination of parts for defects by an SME, which can be expensive, time-consuming and destructive. With the goal of automating the entire process, we have initially focused on surface defects, which are easier to detect with image processing techniques. Using the Leica DVM-6, we can quickly generate large databases of images to process. We developed an algorithm to register images obtained so they had the same chip orientation and positioning. So far, we have ad hoc techniques to detect scratches, texture differences on the surface of the chip, displacements in the identification marking locations, and color variations. We're currently developing approaches based on neural networks to identify scratches in images, and the eventual goal is to develop an entirely automated process that can analyze whole trays of chips at once.

## 37. AUTOMATED NON-DESTRUCTIVE PCB REVERSE ENGINEERING FROM X-RAY COMPUTED TOMOGRAPHY

Domenic Forte, Mark Tehranipoor, Navid Asadi, and Damon Woodard,

In the modern globalized supply chain, reverse engineering (RE) is needed to validate the performance, quality, authenticity, and integrity of electronics, e.g., detection of counterfeits and hardware Trojans. In the case of legacy systems, RE can be an invaluable tool for recovering original design files in order to evaluate, reproduce, and/ or redesign them. The goal of this project is to develop an entirely automated and nondestructive process for the reverse engineering of printed circuit boards (PCBs). X-Ray computed tomography is used to capture a 3-dimensional scan of the entire depopulated board, both external and internal layers. Afterwards, the resultant images are then subject to advanced image processing and machine learning algorithms to intelligently extract the boards' via and trace schematic features. Once the features have been classified and localized, the schematic undergoes vectorization to translate the features from a pixel related information to geometrical information, such as diameter of vias and width of traces. Lastly, the vectorized board information is then exported to a DXF file for the board to be analyzed and/or fabricated. As part of this project, we are currently investigating accurate methods to classify traces and vias, remove noise from presence of high-Z material on the PCB. etc. In future work, we will extract automatically extract component information from optical images of the PCB as well as extend our work on X-ray to populated PCBs.

## 38. BLOCKER: A BIOMETRIC LOCKING PARADIGM FOR IOT AND THE CONNECTED PERSON

Domenic Forte and Damon Woodard,

Biometric techniques offer major advantages over conventional identification and authentication methods, particularly, they are more secure, accurate, reliable, and user-friendly. Nevertheless, they suffer from limitations associated with protecting users' biometric templates against various attacks, e.g., template theft, illegal system access, etc. Unfortunately, existing countermeasures are also extremely limited. This motivates us to develop a framework called BLOcKeR - Biometric Locking by Obfuscation, Physically Unclonable Keys, and Reconfigurability, which combines biometrics and configurability with two recent advances in hardware security, namely

physically unclonable functions (PUFs) and hardware obfuscation. In this regard, a PUF - an object's fingerprint - is incorporated to tie a device (i.e., an integrated circuit) to the biometrics of its owner. Moreover, hardware obfuscation is used to "lock" the hardware from the gates up to the firmware such that it behaves inappropriately without a biometric-dependent key. Besides unique benefits such as configurability and non-linkability, BLOcKeR requires no template storage, contrary to traditional biometric systems. These enhancements make BLOcKeR resistant to various attacks, according to our security assessment. As a first step, we have considered enrollment of a device to one user, whereas our future work shall focus on extending BLOcKeR to multi-user environments (e.g., the family laptop).

## 39. CARDIOVASCULAR BIOMETRIC AUTHENTICATION, KEY GENERATION, AND PRESENTATION ATTACKS

Domenic Forte and Damon Woodard

Cardiovascular signals, such as electrocardiogram (ECG) and photoplethysmograph (PPG), have been investigated as biometrics for the last decade and owe their initial popularity to anticipated spoofing resistance. In this project, we have investigated the following: (1) Methods for secure and reliable ECG-based key generation - our approaches quantize ECG signals into keys based on tunable reliability and entropy parameters. To reduce the need to enroll users over long periods of time and conditions, we also model various noise sources affecting ECG. Our approaches have achieved keys with lengths 300-500 bits for normal ECGs and 98% key reproducibility; (2) First investigation of PPGbased human authentication and recognition based on non-fiducial features; (3) First ever presentation attacks on ECGbased biometric systems - in over 2,500 simulation experiments, our approaches successfully spoofed ECGs 96.7% and 91.78% of the time for fiducial and non-fiducial feature extraction methods and with only one heartbeat of the victim; and (4) Obfuscation-based biometric systems – to protect biometric templates/systems from theft and fault injection, we are using biometric keys to lock/unlock hardware obfuscated systems. In future work, we plan on implementing our quantization methods and presentation attacks in FPGA, reducing the cost of ECG pre-processing through better understanding of noise, and developing countermeasures to ECG presentation attacks.

#### 40. CIRCUIT EDIT ENABLED TRUSTED FABRICATION FOR LOW VOLUME PRODUCTS

Domenic Forte, Mark Tehranipoor, and Navid Asadi

The modern trend of off-shoring semiconductor foundries has led to a decrease in costs and turn-around time for state-of-the-art IC designs. However, this has also created lack of control and trust in the fabrication process, with threats such as IP piracy and Trojan insertion arising as serious concerns, especially for critical applications such as aerospace and military. In order to mitigate such threats, various design protection schemes against an untrusted foundry have been proposed. However, they suffer from high costs, non-trivial overheads, and new attack vectors. Towards this end, we are investigating new techniques that leverage post-fabrication circuit edit for design obfuscation and low-volume trusted fabrication. In this approach, gate-level netlists and layouts are modified and an obfuscated design is fabricated at the untrusted foundry. Circuit edit technologies, along with appropriate layout features, are then used to recover the intended functionality of the design at a trusted facility, thereby preventing the foundry from pirating the design. Initial design obfuscation techniques were presented at ICCAD '16, where we showed that it is possible to make minimal changes to the design with circuit edit constraints, while ensuring that an untrusted foundry is unable to identify the changes made. We are now currently investigating reliability issues that may arise due to circuit edit - by performing focused ion beam (FIB) modification on chips fabricated at advanced nodes, and how to mitigate them a priori during the design stage.

# 41. COVERT GATES: PROTECTING INTEGRATED CIRCUITS FROM REVERSE ENGINEERING WITH UNDETECTABLE CAMOUFLAGING

Domenic Forte and Mark Tehranipoor

Existing methods of camouflaging are based on logic gates that assume one of many Boolean functions, either through variation of threshold voltage or contact configurations. Unfortunately, such methods lead to high overheads, and are vulnerable to invasive as well as non-invasive functional attacks. We have developed a new camouflaging strategy, termed as 'covert gate', that leverages doping and dummy contacts to create camouflaged gates that are indistinguishable from regular gates under modern imaging techniques. The technique allows a designer to introduce arbitrary dummy inputs to logic gates, so that the netlist retrieved by the attacker during reverse engineering is functionally incorrect. Since covert gates are

indistinguishable from regular gates, attack complexity is significantly increased and with very low overheads. In preliminary work, we have fabricated and imaged test structures to show the indistinguishability of the channel and contact regions that are modified to create covert gates. Our empirical results show that covert gate indistinguishability can make SAT attacks exponentially more complex and prevent gate identification by ATPG-based attacks even under pessimistic assumptions. We have also developed models to characterize gate-level overheads, and netlist modification tools for camouflaging designs. In the future, we plan to fabricate prototype devices to validate our models. estimated overheads. indistinguishability of gates in silicon. We also plan to improve our covert gate insertion methods to meet different objectives (minimize area, performance, or power overheads, maximize security, etc.).

# 42. DEVELOPING LOW COST ELECTRICAL TEST METHODS FOR COUNTERFEIT FPGA DETECTION

Domenic Forte and Mark Tehranipoor

Counterfeit components do not possess the same specifications as genuine parts, and can impose significant vulnerabilities and threats to the systems in which they are placed. Reports show that recycled and remarked ICs comprise 80% to 90% of all counterfeits in circulation worldwide. Hence, significant work has aimed to develop low cost and less time-consuming electrical test methods to detect such counterfeits. Programmable ICs are in top 5 counterfeit list and FPGA holds a good portion of it. In this project, we have developed effective test methods for recycled FPGA detection based on supervised and unsupervised machine learning algorithms. We developed a sophisticated ring oscillator design and voltage scaling based fingerprint of FPGA logic cells to exploit degradation. The unsupervised method requires very little (if any) golden information and is effective in the case of legacy chips. We examined the proposed methods for Spartan-3A and Spartan-6 FPGAs, and the result shows that both methods can detect most recycled FPGAs which have experienced accelerated aging for at-least 12 hours. In future, we plan on extending our approaches for detecting remarked FPGAs.

# 43. EMFORCED: EM-BASED FINGERPRINTING FRAMEWORK FOR COUNTERFEIT DETECTION ON REMARKED AND CLONED ICS

Domenic Forte and Mark Tehranipoor

Counterfeit detection techniques often suffer from high cost, device overhead, and testing time. EMFORCED introduces an electromagnetic-based counterfeit detection framework which can be utilized by several entities with no prior knowledge of the devices under test. As our method does not require test vectors, but rather relies on extracting an electromagnetic fingerprint from the circuit only excited by clock, power, and ground inputs. By utilizing statistical analysis methods and machine learning techniques, we demonstrate high-accuracy classification with, or without, a golden reference. EMFORCED offers a low-cost, fast, and zero overhead solution to differentiating between designs.

# 44. EMFORCED: EM-BASED FINGERPRINTING FRAMEWORK FOR REMARKED AND CLONED COUNTERFEIT IC DETECTION USING MACHINE LEARNING CLASSIFICATION

Domenic Forte and Mark Tehranipoor

Electronics supply chain vulnerabilities have broadened in scope over the past two decades. With nearly all IC design companies relinquishing their fabrication, packaging, and test facilities, they are forced to rely upon companies from around the world to produce their ICs. This dependence leaves the electronics supply chain open to counterfeiting activities. EMFORCED, an electromagnetics-based fingerprinting framework, is designed to detect remarked and cloned counterfeit ICs. Benefiting from naturally occurring electromagnetic second order effects to identify the IC design layout without decapsulating the chip under test. Enabling only the clock, power, and ground pins allows us to generate a designspecific fingerprint which is dependent upon the physical parameters of the chip under test. Leveraging the emissions from the clock distribution network creates a holistic, designlevel, fingerprint including both temporal and spatial information. Statistical analysis and machine learning techniques are used to demonstrate reference-free and referenceinclusive classification methods based on EMFORCED measurements, providing various scenarios for this low-cost, fast, and zero design overhead solution.

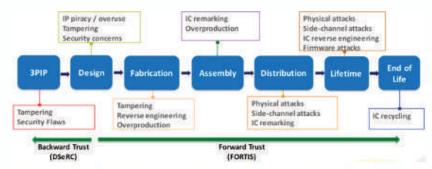

# 45. FORTIS: ESTABLISHING FORWARD TRUST FOR PROTECTING IPS AND ICS IN TODAY'S COMPLEX SUPPLY CHAIN

Mark Tehranipoor, Domenic Forte, Fahim Rahman, and Farimah Farahmandi

Growing complexity of system-on-chip (SoC) and ever-increasing cost of IC fabrication have forced the semiconductor industry to shift from a vertical business model to a horizontal model. In this model, most entities involved in SoC design flow are located across the globe and original intellectual property (IP) owners do not have the ability to monitor and control the SoC design flow. The lack of trust and transparency/ control has led to vulnerabilities such as IP piracy, IC overproduction, etc. The main objective of this project is to develop a comprehensive framework, named FORTIS for detection and prevention of all the mentioned supply chain issues. We have completed the following tasks for the implementation of FORTIS framework,

- 1. Developed and implemented attack-resistant logic obfuscation techniques

- 2. Developed and implemented a locking mechanism which enables structural testing without the need of activating the chip

- 3. Developed and implemented a locking mechanism which enables structural testing without the need of activating the chip

- 4. Developed a hybrid mechanism of IP encryption and logic obfuscation to prevent IP tampering, cloning, and overuse

- 5. Developed the concept of Trusted Authentication Platform (TAP) to address issue like recycling, remarking, and out-of-spec/defective ICs

- 6. Secure key exchange for IC/IP metering

#### Future research plans:

- 1. Implement logic obfuscation techniques which is resilient to state of the attacks e.g., SAT attack

- 2. Implementation of the TAP module

- 3. Implementation of unique key for every chip